|

Hi there! I am an MS/PhD student at Cornell University. I work with Prof. Zhiru Zhang on Electronic Design Automation, Domain-Specific Language for hardware design, and hardware accelerators.

|

|

|

|

|

|

M.S./Ph.D. in Electrical and Computer Engineering |

|

|

B.Eng. in Telecommunication Engineering |

|

|

|

|

|

Exempt Tech Employee |

|

|

Research Assistant |

|

|

MITACS

Research Intern |

|

|

My research interests include EDA (Electronic Design Automation) for FPGA, DSL (Domain-Specific Language), and efficient machine learning. |

|

Debjit Pal, Yi-Hsiang Lai, Shaojie Xiang, Niansong Zhang, Hongzheng Chen, Jeremy Casas, Pasquale Cocchini, Zhenkun Yang, Jin Yang, Louis-Noël Pouchet, Zhiru Zhang DAC 2022 Invited Paper, to appear | paperWe first explain the advantages of the decoupled programming model and further discuss some of our recent efforts to enable a robust and viable verification solution in the future. |

|

Tianchen Zhao, Niansong Zhang, Xuefei Ning, He Wang, Li Yi, Yu Wang CVPR 2022, paper | website | slides | poster | videoWe propose a flexible 3D Transformer on sparse voxels to address transformer's generalization issue. CodedVTR (Codebook-based Voxel TRansformer) decomposes attention space into linear combinations of learnable prototypes to regularize attention learning. We also propose geometry-aware self-attention to guide training with geometric pattern and voxel density. |

|

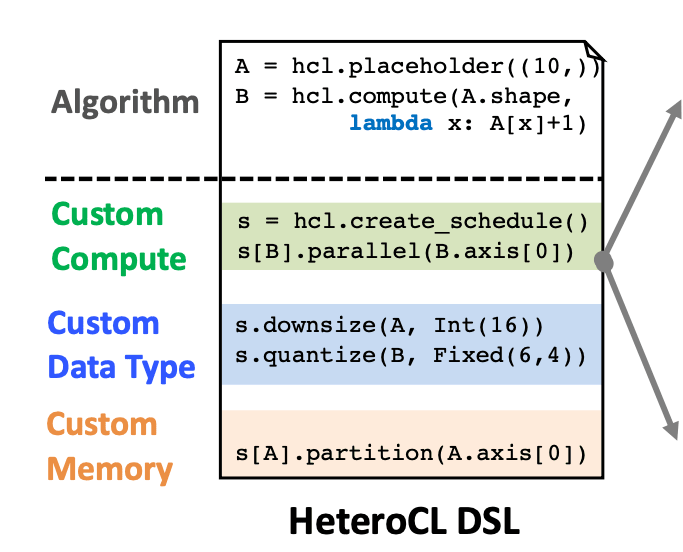

Shaojie Xiang, Yi-Hsiang Lai, Yuan Zhou, Hongzheng Chen, Niansong Zhang, Debjit Pal, Zhiru Zhang FPGA 2022, paper | codeWe propose an FPGA accelerator programming model that decouples the algorithm specification from optimizations related to orchestrating the placement of data across a customized memory hierarchy. |

|

Niansong Zhang, Xiang Chen, Nachiket Kapre TRETS 2022, paperWe extend the previous work on RapidLayout with cross-SLR routing, placement transfer learning, and placement bootstrapping from a much smaller device to improve runtime and design quality. |

|

Xuefei Ning, Changcheng Tang, Wenshuo Li, Songyi Yang, Tianchen Zhao, Niansong Zhang, Tianyi Lu, Shuang Liang, Huazhong Yang, Yu Wang Arxiv Preprint, paper | codeWe build an open-source Python framework implementing various NAS algorithms in a modularized and extensible manner. |

|

Niansong Zhang, Xiang Chen, Nachiket Kapre FPL 2020, paper | code

We build a fast and high-performance evolutionary placer for FPGA-optimized hard block designs that targets high clock frequency such as 650+MHz. |

|

|

|

|

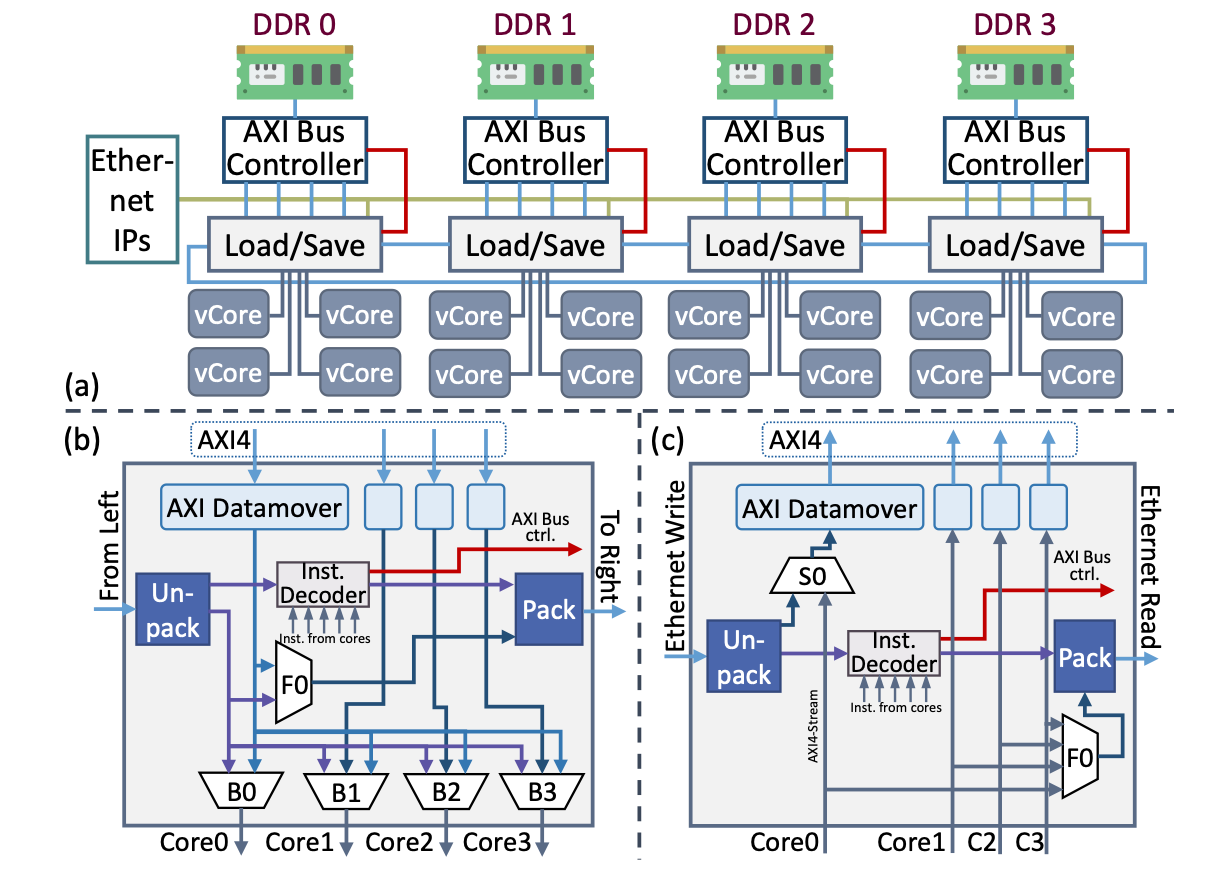

Shulin Zeng, Guohao Dai, Niansong Zhang, Yu Wang MICRO 2021 ASCMD Workshop, paper | videoWe propose a multi-node and multi-core accelerator architecture and a decoupled compiler for cloud-backed INFerence-as-a-Service (INFaaS). |

|

Student Volunteer: FCCM’22 |

|

DAC Young Fellow 2021 FPL 2020 Best paper Nomination (Michal Servit Award) Outstanding Bachelor Thesis Award | Sun Yat-sen University Mitacs Globalink Research Internship Award | Mitacs, Canada First-class Merit Scholarship x2 | Sun Yat-sen University Lin and Liu Foundation Scholarship | SEIT, Sun Yat-sen University |

|

Niansong Zhang, Songyi Yang, Shun Fu, Xiang Chen, "Industry Profile Geometric Dimension Automatic Measuring Method Based on Computer Vision Imaging." Chinese Patent CN201811539019.8A, filed December 17, 2018, and issued April 19, 2019. Niansong Zhang (at Novauto Technology), "A Pruning Method and Device of Multi-task Neural Network Models", Chinese Patent 202010805327.1, filed August 12, 2020. |